- 概述

- 理由

- 解答问题

- 应用指南

- 发表文章

随着集成电路工艺技术的不断提高,晶体管的特征尺寸及刻蚀沟槽不断减小,沟槽及其侧壁的镀膜技术面临严峻的挑战,物理气相沉积(PVD)及化学气相沉积(CVD)工艺已经无法满足极小尺寸下良好的台阶覆盖要求,而控制纳米级别厚度的高质量超薄膜层制备也成为技术难点。

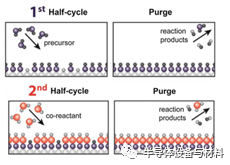

原子层沉积(ALD)是一种可以将物质以单原子膜的形式,一层一层镀在基底表面的先进沉积技术。一个ALD循环包括两个先后进行的半反应(图1)。在一定的真空环境下,前驱体和共反应物交替地通入反应腔体,饱和吸附并在衬底表面发生化学反应形成单原子层。每个半反应间通入惰性气体进行清洗,确保完全除去过量的反应物和生成的小分子副产物。理论上,经过一个循环工艺,基底表面便镀上了一层单原子膜。通过增加循环次数,原子层将依次沉积在表面上,形成薄膜。

图1 单个原子层沉积工艺的循环过程

由于前驱体和共反应物的化学吸附(化学反应)自限制性,运用ALD技术可以大面积沉积均匀无孔的超薄膜,在亚纳米尺度上精确控制膜厚,并且在高深宽比、形状复杂的结构中具有优异的保形性。ALD沉积薄膜的温度窗口很宽,反应对生长温度并不敏感,因此它可以适应不同温度环境下的薄膜制备。鉴于ALD的工艺特点和沉积薄膜的诸多优势及特征,近年来获得了研究人员和企业各界的广泛关注,尤其是在半导体产业发挥越来越重要的作用。

目前,对于金属、金属氧化物、氮化物、碳化物、硫化物、氟化物的原子层沉积研究卓有成效。ALD在半导体先进制程中主要的应用包括金属栅、栅介质层和互连线扩散阻挡层加工工艺三个方面。

金属栅:在新一代制程中,原有的半导体多晶硅栅极将被金属取代以消除层间损耗,而此处金属沉积可选用ALD工艺完成。

1. P型半导体

Ru作为P型半导体栅极的ALD工艺相对成熟,主要是在NH3等离子体的还原作用下将前驱体材料包括RuCp2(Cp=环戊二烯基)、Ru(EtCp)2(Et=乙基)还有Ru(od)2(od=辛二酮)、Ru(thd)3(thd=2,2,6,6-四甲基-3,5-庚二酮)在NH3还原作用下生成金属Ru或者是在O2的作用下将前驱体氧化为RuOx。虽然Ru前驱体种类众多,但是由于Ru金属本身属于惰性材料,所以一旦吸附在硅片背面会很难除去。然而在实际生产中,CMP过程会不可避免地诱导金属栅极在背面的污染,对CMOS生产的前端非常不友好,所以Ru作为金属栅极的应用受到了限制。

TiN是P型半导体栅极的理想材料,不仅电阻率低、工艺兼容性好,而且还和栅极介质层HfO2有良好的热稳定性。1988年,Hiltunen等人率先对ALD沉积TiN的工艺进行了研究,通过使用TiCl4作为前驱体NH3做共反应物,500℃下能够在玻璃上均匀沉积多晶TiN,但是沉积速率只有0.02nm/循环。此外,还有研究使用TiI4作为前驱体,和TiCl4相比其沉积温度能够下降至350℃,其沉积速率也有明显改善。

但是如果要实际应用在CMOS的工艺,以上的沉积速率还远远不够,主要原因在于共反应物NH3提供的N成分远远不够Ti-N键的连接,所以研究者们开发了作为TEMAT(Ti[N(C2H5CH3)2]4)新型前驱体,使反应窗口能够降低至150-220℃,沉积速率也提高为原先的10倍。以上的研究为TiN作为金属栅极提供了良好的技术基础,迄今仍然主要使用上述提到的前驱体作为研究方向。

2. N型半导体

和P型半导体相比,用ALD沉积N型半导体更为困难,最早的研究开始于2007年,Triyoso等人用PEALD沉积了TaCy薄膜,在此基础上开展了对TiAlC和TaAlC的研究。

TiAlC一般是以TiCl4作为作为Ti前驱体,以TMA (三甲基铝)作为Al前驱体,一个完整的沉积过程由脉冲TiCl4--吹扫N2--脉冲TMA--吹扫N2组成,最终能够形成粗糙度只有0.33nm的无定形膜层,通过C-V测试可知缺陷很少,唯一的缺点是和高性能nMOSFETs相比,这种方法得到的EWF shift很小。通过把Al前驱体从TMA更换为TEA(三乙基铝),TEA提供了更多的β-H能够有效清除H2,提高Al的生成效率,因而被广泛使用。

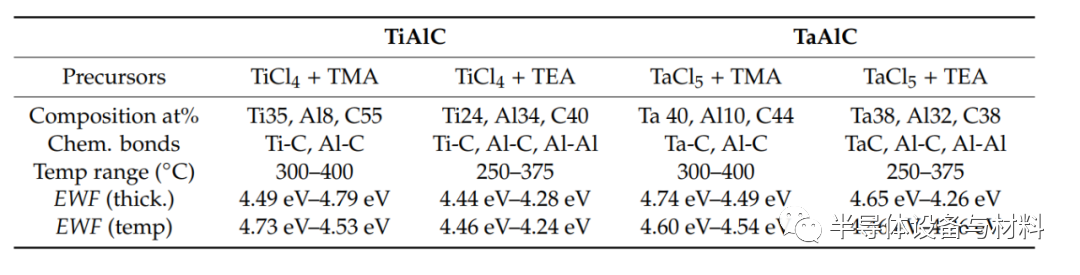

TaAlC一般是用TaCl5作为作为Ti前驱体,TMA、TEA作为Al前驱体,从表一其实可以看出,两种材料的沉积工艺和性能都非常相似。

表一:TiAlC和TaAlC层的工艺对比

栅介质层:

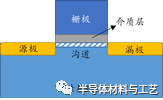

在集成电路产业史上,为了追逐摩尔定律,MOSFET(图2)的特征尺寸不断缩小,工作电压也不断降低。为了抑制短沟道效应,减小栅介质层对提高栅电容以提高栅对沟道的控制能力,调节阈值电压起着至关重要的作用。在传统MOS器件中,通过简单的氧化工艺可以在Si衬底上得到一层所需厚度的SiO2层作为栅介质层。当集成电路器件特征尺寸进入180nm时,栅氧化层的厚度小于3nm。由于P型掺杂多晶硅栅的硼穿透效应日益严重(硼在SiO2介质中属于快扩散物质),半导体业界在氧化工艺中加入NO、N2O和NH3等含氮气体以形成更致密的SiON介质层改善纯SiO2的不足。

随着技术节点的跟进,当制程工艺特征线宽要求小于45nm,相应的SiO2层厚度将缩小至1nm以下,此时量子隧穿效应的影响将急剧增加——以NMOS为例,衬底的电子以量子形态大概率地穿过栅介质层进入栅,导致栅漏电十分严重。通过改善氧化工艺提高介质层氮含量以及减小SiO2厚度的方法继续缩小MOS器件难以为继,开发新工艺制备新材料以代替SiO2和SiON十分重要。

在集成电路的发展历程中,选用比SiO2介电常数(3.9)更高的高k材料成为解决这一技术瓶颈的关键一招。高k材料的选择除了具有高的介电常数外,还需满足宽禁带、与衬底材料间足够的能带偏移量和低的界面态。

绝大多数高k材料的加工工艺都依赖于原子层沉积技术。此前,基于ALD沉积的一些重要研究包括TiO2、HfO2、Al2O3、ZrO2、Ta2O5,稀土元素氧化物和一些硅酸盐混合的纳米层状结构材料。Si3N4、Al2O3介电常数仍较低。TiO2虽然介电常数很高(80),但禁带宽度小且与衬底明显的界面缺陷限制了其作为栅介质的应用。HfO2的介电常数为25,具有适合的禁带宽度(5.8eV),综合各方面性能要求,高k材料HfO2作为栅介质层得到了业内广泛的认可和应用。

图2 MOSFET结构示意图

互连线扩散阻挡层:

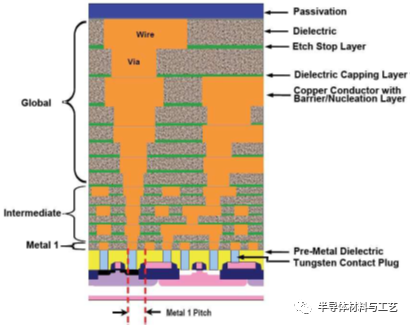

摩尔定律导致芯片中功能密度的增加,定义了每个芯片区域中互连设备的数量。随着IC的最小特征尺寸减小,有源器件密度增加。由于芯片表面上互连线所占据的面积比容纳有源器件所需的面积扩展得更快,因此器件集成变得更加苛刻。最终,最小的芯片面积受限于互连技术。这一问题是通过多层互连系统解决的,其中互连线所需的区域在两个或更多层之间共享(图3)。

微处理器单元(MPU)中有源器件的功能密度非常高,金属级的数量有望达到1216。此外,随着栅极数量增多,栅极之间需要更多的连接,互连线的平均长度将增加。如果不包括全局电线,则MPU中互连的总长度预计将超过2 km / cm2。在1990年代后期,很明显地发现,互连长度的增加导致互连的电阻乘以电容(RC)时间延迟的增加,并且在四分之一微米的设备节点中,传播延迟超过了固有延迟。

除RC延迟外,由于铝对电迁移的敏感性强,随着电流密度的增加,传统的铝金属化也面临着巨大的挑战。因此,铜因其较高的电迁移电阻和低电阻率逐渐取代铝工艺称为互联技术的主流技术。

互连工艺中需要使用一层阻挡层金属,它可以增强铝铜合金互连线附着在硅化物上的力,减小互连线与接触孔之间的接触电阻和应力,氮化钛还可以防止硅与铝之间相互扩散,避免铝穿刺。铝工艺中的阻挡层金属是钛(Ti)和氮化钛(TiN)。高温时Cu在Si中扩散系数较高,铜原子一旦进入硅器件,便会成为深能级受主杂质产生复合中心,使载流子寿命降低,从而导致器件失效。因此在铜互连结构中阻挡层金属更为必须。铜的阻挡层金属是钽(Ta)和氮化钽(TaN)。

随着工艺技术的不断发展,线宽的减小使得铜线的阻抗上升,电路的RC特性降低,RC延时增加。解决这一问题的最简单办法就是降低扩散阻挡层的厚度。阻挡层金属的厚度不断变薄,钽和氮化钽作为阻挡层金属的阻挡性能比钛和氮化钛好,所以在铜工艺中利用氮化钽代替氮化钛。利用PVD技术沉积的氮化钽是工业上应用最多的技术,它能较好地控制N/Ta比。

但是由于PVD沉积流量的方向性和对多数金属的高粘结系数,导致制备薄膜不连续,台阶覆盖率低。CVD存在镀制薄膜较厚,成分不纯等内在缺陷。通过ALD过程,在器件尺寸小于100nm和较低的温度下,能够得到阶梯覆盖率高,原子层厚度较薄且可精确控制的铜扩散阻挡层。

目前ALD TaN技术用于铜互连阻挡层被广泛的研究。早在2002年,Kim等人利用plasma-enhancedALD的方法用TaCl5,氢气和氮气等离子体在硅基底上沉积TaN薄膜。随后Kim等人使用Ta金属有机物前驱体和氢等离子体技术生成了坚固且超薄的TaNx铜扩散阻挡层,定量研究了扩散阻隔性能,并且提出该层优异的阻挡性能归因于膜的纳米晶体微观结构。

Furuya等人用Ta(N(CH3)2)5和He/H2等离子体沉积了富Ta的TaN粘合层,克服了由于ALD阻挡层金属与Cu之间低粘附性导致的通孔产量低的问题。Dey等人研究发现,在10nm节点以下的工艺技术中,当其他的金属如钌取代铜作为互联金属,ALDTaN仍能表现出优异的阻挡层性能。但是由于ALD存在生长速度较慢等问题,目前半导体产业中铜互连阻挡层仍然采用PVD的方法。但是由于ALD技术拥有PVD和CVD所无法比拟的优势,在科技工作者的共同努力下,ALD扩散阻挡层最终会被大规模应用。

图3 MPU器件分级放大横截面图

来源个人图书馆 leafcho